# NETWORK THEORY

## LECTURE 7

**SECTION-D:NETWORK SYNTHESIS**

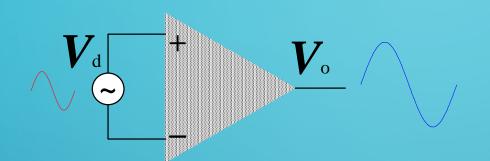

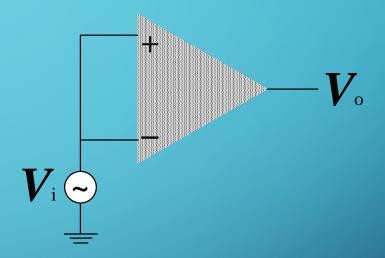

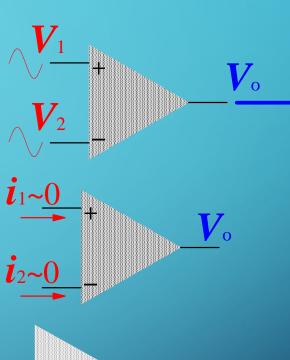

## DOUBLE-ENDED INPUT

- Differential input

- $0^{V}$  = V V•  $0^{V}$  phase shift change between  $V_{o}$  and  $V_{d}$

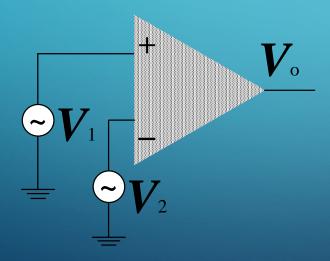

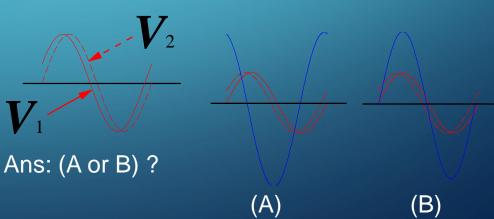

Qu: What  $V_o$  should be if,

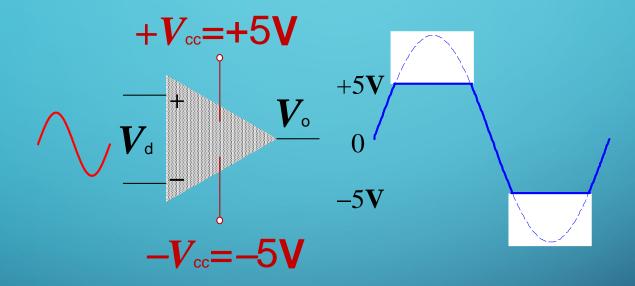

## DISTORTION

The output voltage never excess the DC voltage supply of the Op-Amp

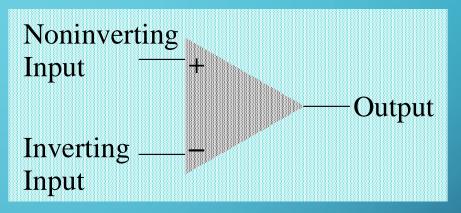

### **COMMON-MODE OPERATION**

- Same voltage source is applied at both terminals

- Ideally, two input are equally amplified

- Output voltage is ideally zero due to differential voltage is zero

- Practically, a small output signal can still be measured

Note for differential circuits:

Opposite inputs : highly

amplified

Common inputs: slightly

amplified

⇒ Common-Mode Rejection

## COMMON-MODE REJECTION RATIO (CMRR)

Differential voltage input:

$$V_d = V_+ - V_-$$

Common voltage input:

$$V_c = \frac{1}{2}(V_+ + V_-)$$

Output voltage:

$$V_o = G_d V_d + G_c V_c$$

G<sub>d</sub>: Differential gain

G<sub>c</sub>: Common mode gain

Common-mode rejection ratio:

CMRR =

$$\frac{G_d}{G_c}$$

=  $20\log_{10}\frac{G_d}{G_c}$  (dB)

Note: When  $G_d >> G_c$  or CMRR  $\to \infty$  $\Rightarrow V_o = G_d V_d$

### **CMRR EXAMPLE**

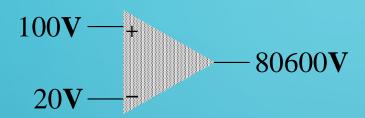

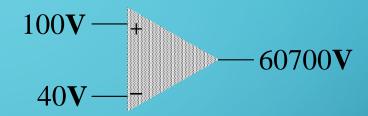

#### What is the CMRR?

#### Solution:

$$V_{d1} = 100 - 20 = 80 \mathbf{V}$$

$$V_{c1} = \frac{100 + 20}{2} = 60 \mathbf{V}$$

$$V_{c2} = \frac{100 + 40}{2} = 70 \mathbf{V}$$

(2)

From (1)

$$V_o = 80G_d + 60G_c = 80600V$$

From (2)

$$V_o = 60G_d + 70G_c = 60700V$$

$$G_d = 1000$$

and  $G_c = 10$   $\Rightarrow$  CMRR =  $20\log(1000/10) = 40$ dB

NB: This method is Not work! Why?

## **OP-AMP PROPERTIES**

#### (1) Infinite Open Loop gain

- The gain without feedback

- Equal to differential gain

- Zero common-mode gain

- Pratically,  $G_d = 20,000$  to 200,000

#### (2) Infinite Input impedance

- Input current  $i_i \sim 0A$

- $T-\Omega$  in high-grade op-amp

- m-A input current in low-grade op-amp

#### (3) Zero Output Impedance

- act as perfect internal voltage source

- No internal resistance

- Output impedance in series with load

- Reducing output voltage to the load

- Practically,  $R_{\rm out} \sim 20\text{-}100 \ \Omega$

$$V_{\text{o}}$$

$V_{\text{o}}$

$V_{\text{o}}$

$R_{\text{load}}$

$V_{\text{load}}$

$V_{\text{load}}$

$V_{\text{load}}$

$V_{\text{load}}$